Martin Andraud

Assistant professor

UCLouvain (BE) & Aalto University (FI)

Contact: martin.andraud [at] uclouvain [.] be

Research interests

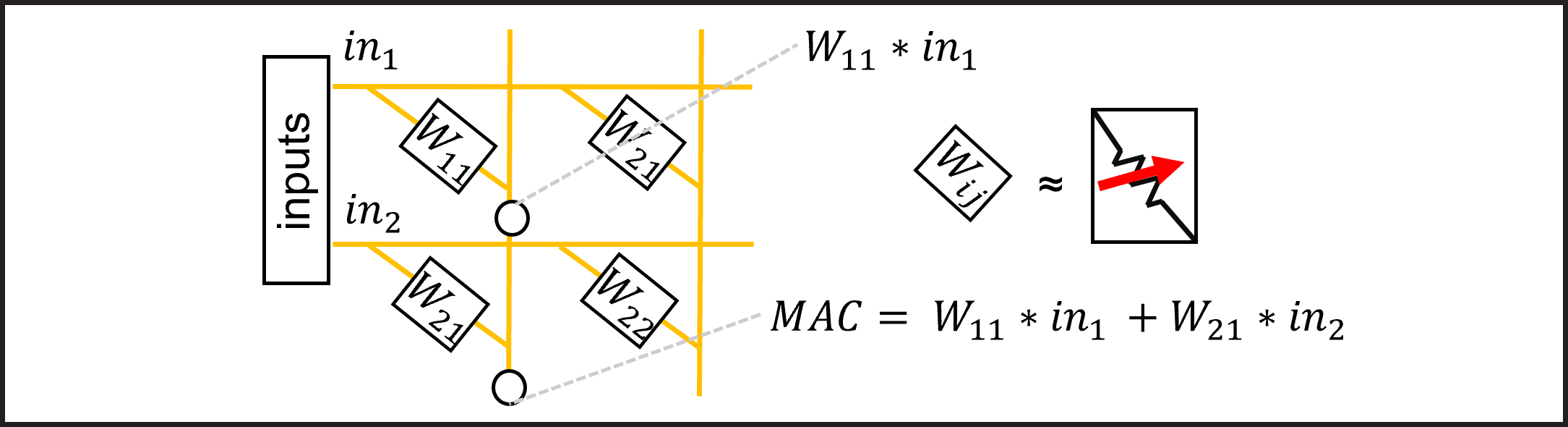

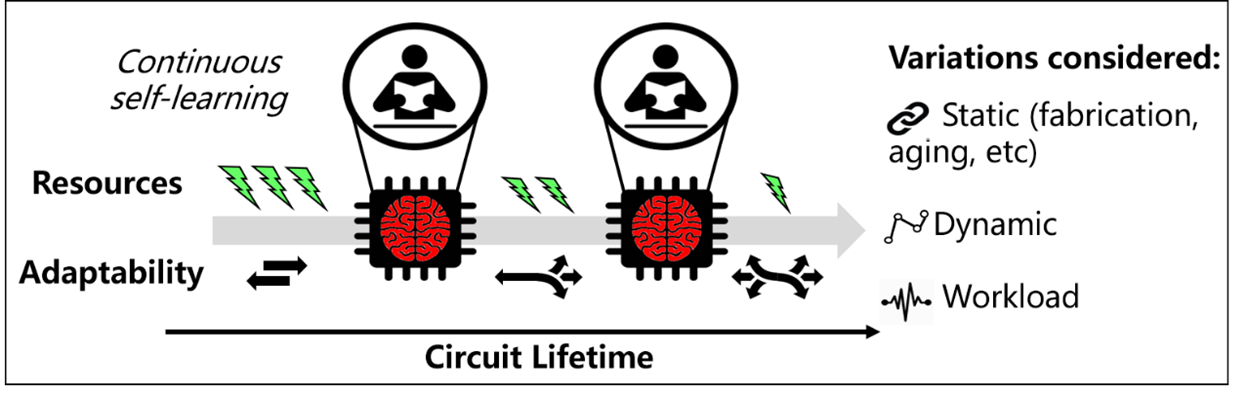

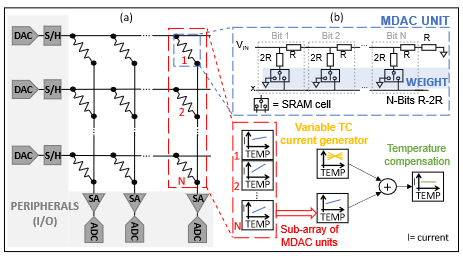

Processors (accelerators) for edge AI and Tiny ML 100%About me

I am an assistant professor at UCLouvain, Belgium, since January 2024, and a visting professor at Aalto University, Finland. My research interests include ASIC design for alternative AI tasks (e.g., neurosymbolic AI, or probabilistic AI) and online calibration/adaptation methodologies for reliable mixed-signal AI DNN accelerators, in particular based on emerging memory technologies.

I obtained my doctoral degree in TIMA lab, Grenoble-Alpes University, France, in 2016, supervised by Emmanuel Simeu and Haralampos Stratigopoulos. I then worked as a post-doc successively in TU Eindhoven and KU Leuven from 2016 to 2019. Prior to joining UCLouvain in 2024, I was an assistant professor at Aalto University between 2019 and 2023.

I am always interested in collaborating, please do not hesitate to get in touch.